本經驗主要分享串行SPI總線配置的工作經驗,是一種高速的串行總線輸入輸出口。在工業應用廣泛。有三線制和四線制之分,學習使用過程中,常發現有一些配置誤區,導致無法正常通信。

工具/原料

SPI總線

工業通信應用

方法/步驟

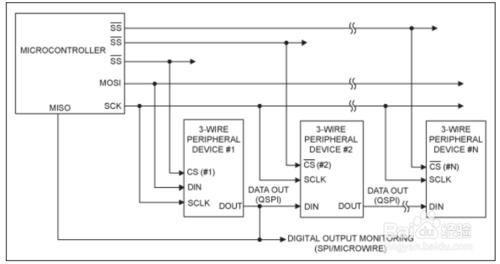

SPI總線有三線制總線(時鐘SCLK,輸入MOSI,輸出MISO)和四線制總線,區別在於四線制多了一個主從機片選/CS或/SPISTE。SPI總線實質上是一個環形總線結構,SCLK為SPI總線的公用時鐘,由主機控制。主要是在sclk控制下,兩個雙向移位寄存器進行數據交換。

在配置SPI口的時候,除了初始化寄存器外,準確配置時鐘極性也是關鍵。這也是在SPI主從機通信時常出現的問題。注意兩點:1.主設備的spi時鐘和極性的配置由外設(從設備)來決定,2.二者的配置應保持一致,即主設備的輸入,輸出和從設備的輸入輸出應保持一致。

但是在硬件的連接上,主設備的輸出MOSI與從設備的輸入連接,輸入與從設備的輸出相連,因而主設備的SPI時鐘極性的配置與從設備接收的極性配置是相反的,跟從設備的發送配置是相同的。

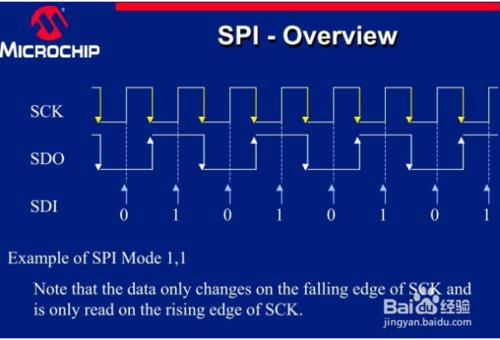

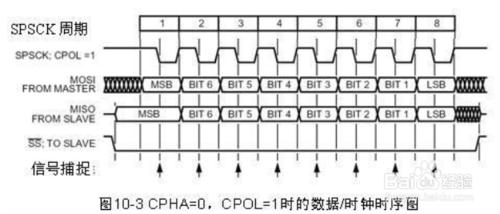

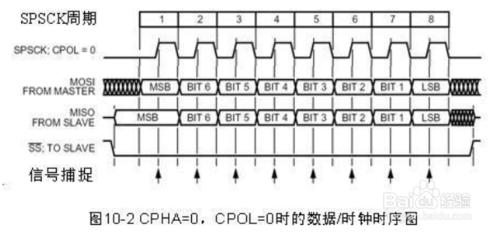

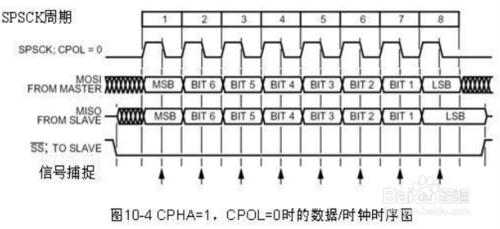

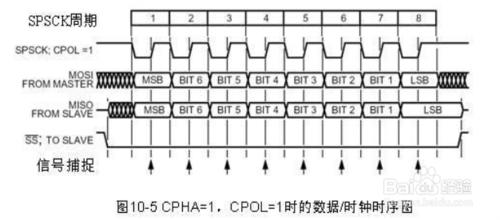

那麼對於其時鐘極性配置又是什麼呢?其實就是時鐘極性和時鐘相位的配置,對應為CPOL/CPHA,按二進制組合可以配置為四種工作時序,為mode0,mode1,mode2,mode3。

也就是說:主設備在時鐘的下降沿發送數據,從設備在時鐘的上升沿接收數據,因而,主設備的SPI時鐘極性應該配置為下降沿有效。

只有時鐘極性和相位配置正確後,數據才能夠被準確的發送和接收。

因而,我們在配置SPI總線的極性時,應避免掉入誤區,容易認為在通信過程中,主從設備的模式一定一致的,主設備配置為mode0,從設備一定配置為0。這種配置方式往往是會出錯的,會使通信不正常。

注意事項

SPI總線

時鐘極性配置誤區