P2.5室內LED全綵電子顯示屏3大技術與4大架構

小間距P2.5室內LED全綵電子顯示屏憑藉著真正的無縫拼接、高性價比、出眾的顯示效果等優點,已經被越來越多地應用在控制室、指揮大廳、會議中心等關鍵場合。

影象拼接處理器的要求

隨著LED顯示屏畫素間距不斷變小,觀看距離不斷拉近,為了達到出色的顯示效果,不但要求LED顯示屏本身在影象處理和拼裝工藝上精益求精,對LED顯示屏前端的影象拼接處理器(以下簡稱拼接器)也提出了更高的要求:

(1)證輸出同步性,避免拼接畫面不同步現象;

(2)優化影象處理演算法,使經過縮放處理的影象保持高清晰度;

(3)自定義輸出解析度,應對LED顯示屏物理解析度不規則的特點。

應用於小間距LED顯示屏的拼接處理技術

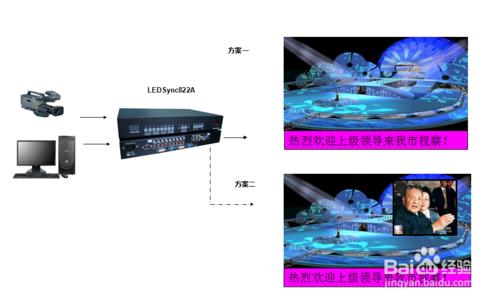

拼接器與小間距LED顯示屏的配合使用

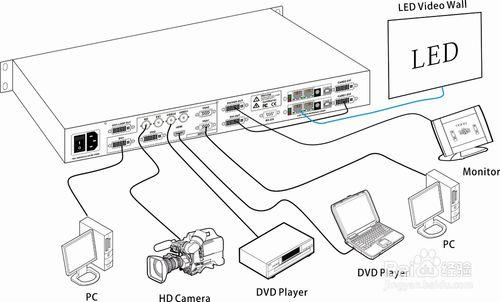

拼接器的一個關鍵應用是可以輸出多路DVI訊號,對矩陣排列的多個顯示屏進行拼接顯示,使之成為邏輯上的一個完整的顯示區域。

對於LED顯示屏而言,我們可以將一臺LED控制器所驅動的顯示區域定義為一個獨立的LED顯示屏,當前的LED控制器採用DVI/HDMI作為訊號輸入介面,支援最大的輸入解析度為1920×[email protected],最大頻寬為165MHz,所驅動的LED顯示屏最大物理解析度為1920×1200。

隨著LED小間距產品的顯示面積越來越大,幾十平方米的專案屢見不鮮,LED顯示屏的物理解析度往往會超過1920×1200,即每一塊超大規模的LED顯示屏,都是由若干個LED控制器所驅動的若干個獨立的顯示區域組成的,對於拼接器的應用而言,只需要對應LED控制器的數量提供若干個DVI輸出介面,並對整個LED螢幕進行拼接顯示即可。

拼接器在小間距LED顯示屏的應用中,有幾個關鍵技術值得關注:

訊號的輸出同步性

拼接器的多路DVI訊號輸出,必然存在訊號的同步性問題。不同步的訊號輸出到LED顯示屏上,在拼接處就會出現畫面撕裂現象,在播放高速運動的影象時尤為明顯。如何保證訊號的輸出同步性,成為衡量一個拼接系統成敗的關鍵。

圖形處理演算法

我們知道,點對點的影象顯示效果是最好的,經過縮小處理後的影象,如果僅採用普通的圖形處理技術或通用的FPGA圖形處理演算法,影象的邊緣會出現鋸齒,甚至會出現畫素缺失,影象的亮度也會下降。而高階的影象處理晶片或利用複雜圖形處理演算法的FPGA系統會最大限度的保證縮小後圖像的顯示效果。因此,好的圖形處理演算法是一款應用於小間距LED顯示屏的拼接器的關鍵技術。

非標準解析度的輸出

小間距LED顯示屏是由一塊一塊相同規格的顯示單元矩陣拼接而成,每個顯示單元尺寸和物理解析度是固定的,但是拼接起來的整個大螢幕,往往不是一個標準的物理解析度。比如,顯示單元的解析度為128×96,只能拼成1920×1152,卻拼不出1920×1080。在超大規模的拼接系統裡,每臺LED控制器所驅動的LED顯示區域可能不是標準的解析度,這個時候,拼接器具有非標準解析度的輸出就顯得關鍵,它可以幫助我們快速找到合適的拼接方式,從而合理的分配資源,有效節約LED控制器和傳輸裝置的使用數量。

應用於小間距LED顯示屏的拼接器

目前拼接器可分為四類,即嵌入式純硬體架構、PCI-E匯流排架構、分散式網路架構、混合架構。

嵌入式純硬體架構

整機結構通常會採用“背板+訊號採集板+主控板+訊號輸出板”的設計,訊號採集板進行諸如視訊採集、縮放、疊加、格式轉換等訊號處理工作,通過背板匯流排將經過處理的訊號傳送給主控板的FPGA訊號處理系統,通過嵌入式ARM系統實現對主控FPGA配置、與上位PC機通訊、系統間的資料交換等功能,通過訊號輸出板將訊號輸出給顯示終端。

純硬體架構拼接器的結構相對簡單、不容易出現系統故障;採集板和輸出板可熱插拔,易於更換;可實現多路、多格式訊號的採集和處理;背板交換式技術和輸出板卡統一時鐘技術確保了多路訊號輸出的同步性;每一路DVI輸出訊號的解析度均可自定義,符合LED顯示屏的拼接特點。

諸多特點使純硬體架構迅速成為當今拼接器領域的主流產品之一。但是,由於採用了FPGA作為核心的影象處理單元,演算法的優劣決定了一款拼接器處理效果的好壞,尤其是影象縮放的演算法,如何進行優化以達到更清晰的顯示效果,已經成為判定純硬體拼接器產品價值的重要指標。

PCI-E匯流排架構

通常匯流排架構的拼接器採用PCIExpress技術,可用資料頻寬高達上百Gbps。主機配備高效能的CPU及大容量記憶體,可根據應用領域的不同預裝不同的作業系統(如64位的Windows7),並可直接執行各種應用程式。拼接器配備多張高效能的圖形輸出卡,每張輸出卡擁有超高的內部頻寬及視訊記憶體,並且所有的輸出影象都被同步以消除顯示單元間的影象撕裂。同時還配有多張輸入卡,支援多種訊號格式,並能夠對輸入訊號進行影象處理。

PCI-E匯流排架構拼接器就是一臺高效能的計算機,所有元件都選用各大硬體廠商最先進和成熟的技術,比如CPU可選用Intel,顯示卡可選用英偉達。所有計算機領域的高新技術也能夠被快速的融合進來。這使得PCI-E匯流排架構拼接器在運算速度、影象處理、操作方式等方面具有無法比擬的優勢。

PCI-E匯流排架構拼接器門檻很低,對於簡單的應用,一臺工控機,加上一個專業的多通道輸出顯示卡即可實現。

另一方面,如何解決系統穩定性問題,如何設計一款直觀且功能強大的控制軟體,如何解決高匯流排頻寬下資料傳輸的各種問題等,都需要強大的研發團隊和雄厚的資金基礎,同時需要經驗的積累。就是說,高階的PCI-E匯流排架構拼接器不但需要滿足訊號採集、處理、拼接等最基本的應用,在系統穩定性、軟體易用性等方面的設計等方面都需要更多的投入,才能使拼接器滿足各種嚴苛的應用環境。

但是要注意,匯流排架構拼接器大多采用Windows作業系統,一旦受到病毒攻擊可能致使系統癱瘓,停止顯示。而且,由於採用了定製的圖形顯示卡,各輸出通道的解析度一般需要符合VESA(視訊電子標準協會)標準,不能定義非標準的解析度輸出,也不能定義每個通道不同的解析度。

分散式網路架構

分散式網路架構拼接器通常採用節點式硬體結構,每個輸入、輸出節點獨立分開,通過雙絞線接入中心交換機,對資料進行互動傳輸。

其核心是一套先進的視訊編解碼技術,通過各種訊號輸入節點,將採集到的DVI、VGA、YPbPr、CVBS、3G-SDI等訊號進行處理和編碼,通過專用的網路通訊協議,將編碼後的視訊流經中心交換機傳輸到輸出節點解碼,並轉換為DVI數字訊號輸出到顯示終端。

輸出節點的同步性成為了該系統應用的關鍵。一種辦法是通過網路直接傳送同步碼,實現多臺輸出節點的同步輸出。但是由於網路誤位元速率的存在,這種方式執行一段時間後,還是會出現輸出不同步現象。另一種辦法是通過SYNC介面將多臺輸出節點進行物理連線,選擇一臺輸出節點作為主機,向其他輸出節點主動傳送同步碼,從而使所有輸出節點同時接收到同步訊號,實現真正的幀同步輸出,確保顯示影象完整,螢幕拼接處無撕裂。

目前分散式網路架構拼接系統的應用越來越多,由於其分散式的特點,便於整個建築裡的綜合佈線和不同區域的多個顯示終端集中管理。配合先進的視覺化軟體的幫助,可向使用者提供人性化、視覺化、綜合化的服務。

但是,受限於頻寬和編解碼技術,分散式網路架構目前還不支援雙鏈路DVI數字訊號和HDMI訊號的接入。同時,由於編碼、處理、解碼、訊號同步輸出等環節均需要幀快取,因此在資料的實時性方面與其它幾種拼接技術相比存在差距。另外,在需要顯示的點對點數超過1920×1200解析度的影象時(需要兩臺以上的訊號輸入節點),無法保證多路同步源輸入訊號的再同步輸出。

混合架構

混合架構,一般指以上三種拼接技術之中的兩種或兩種以上相結合的拼接器或拼接系統。

比如PCI+硬體背板匯流排架構拼接器,它的系統控制和影象處理分別獨立實現。PCI匯流排負責系統控制,並在後臺執行作業系統;硬體背板匯流排負責視訊影象處理,系統允許對大量的高解析度輸入訊號進行同步處理,同時仍能在全幀速下保持實時的操作效能和最佳的影象質量,同時確保輸出訊號的同步性。針對重要應急場所,可以確保永不黑屏,即便PCI匯流排負責的作業系統發生故障或病毒感染,通過專用的背板圖形處理匯流排,也能夠確保任何時刻顯示外來視訊影象。

通過混合架構,可以綜合應用,取長補短,極大地增加了系統的穩定性。這也是今後拼接技術的發展方向,具有更為廣闊的應用空間。

小間距P2.5室內LED全綵電子顯示屏的應用

目前,小間距LED顯示屏的應用很廣泛,它包括但不限於:

·軍隊演習指揮系統

·公共安全顯示指揮系統

·電力排程系統

·交通路網及航空監控顯示系統

·能源行業生產排程系統

·政府及企事業單位會議顯示系統

·廣播電視傳媒顯示系統

·公共場所資訊釋出系統

作為新一代背景牆顯示終端,小間距LED顯示屏正在為各行各業的關鍵系統提供優質的服務。