時鐘電路是MCU正常工作的保障,為MCU提高時鐘,一個小小的晶振的設計電路也是很有講究的,正好最近在調試MCU芯片的最小系統電路,現在就結合最近的調試經歷簡單的分享下我的經驗。

工具/原料

mcu時鐘電路設計調試

晶振

方法/步驟

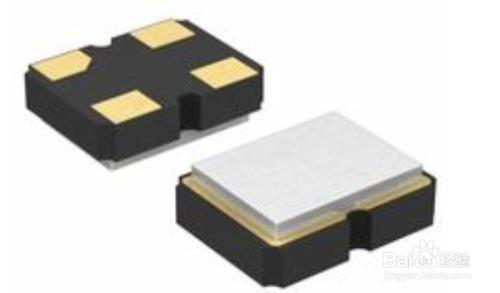

晶振可以分為有源晶振和無源晶振,就經驗而言,使用有源晶振的效果會有些。有源晶振一般有4個pin,多為貼片;無源晶振為2pin,多為插裝。

一般在MCU設計的時候,多使用的是有源晶振,根據晶振的datasheet,我們可以得到兩個很重要的參數,分別為負載電容load Capacitance(Cl)

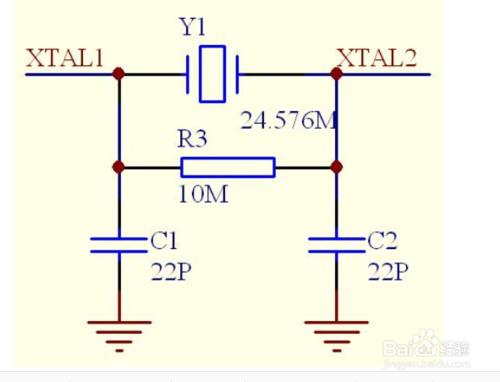

例如在進行MCU的調試工作時,採用如上圖所示的時鐘電路,發現起振時間,時鐘的幅度(clock amplification)和並聯電阻和較大的關係,甚至會影響到晶振的正常工作。

在晶振電路上並聯大電阻的目的是為了提高Q值,增大晶振的電流,使其更易起振,因而對該並聯電阻的選取是需要調試來確定的,當然,大部分情況下,省去也是可以起振的。

關於正確選取晶振引腳的兩個電容。一般情況下,該值可由負載電容和內部電容,PCB板上電容確定。串聯兩個電容是為了匹配負載電容,因而有公式

晶振的負載電容

Cl=[(C1*C2)/(C1+C2)]+Cic+△C

一般C1=C2